There are, however, no illusions about some of the challenges or obstacles that have to be addressed, he added.

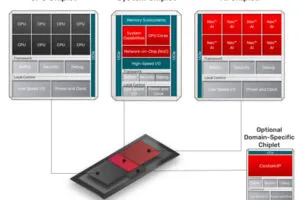

The first of these is interoperability and standards. Access to chiplets is essential to design any complex, large system, Chakraborty told Electronics Weekly shortly after participating in a chiplets panel discussion at DAC. “While there are many vendors, the customer has to various tradeoffs, such as cost, which package to use, 2.5D or vertical stacking, thermal issues and power profiles, as well as how to model and how to represent them,” he said.

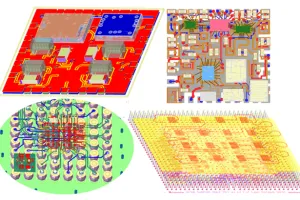

Tools like 3DIC Compiler offer system level performance analysis including software, hardware, core design analysis, he continued. Customers can plug and play different components and, use abstractions to evaluate the different options. Even then, some customisation may be needed, with extensions for a particular application, for example.

Standards and interoperability are another challenge. “Standards are extremely important not only for die-to-die interfaces but for UCIe (Universal Chiplet Interconnect Express),” said Chakraborty. UCIe is not the only standard but in terms of die-to-die interfaces it is the most prevalent, he added.

Once tested and assembled, the chiplet has to be integrated which requires multiple physics analysis using compiler tools. Commenting just before Synopsys completed the deal to acquire ANSYS, Chakraborty said, “ANSYS analysis tools are really the golden standard in the industry for thermal, for higher drop multi physics” and explained that an environmental platform that accommodates the end customer using multi-die and chip, would be critical.

“One thing that comes with chiplets is that they are far more complex than soft IP . . .the chip will contain IP, so they are more complex kind of components. . . And the IPS come from different vendors.

“Now you’re talking about dealing with licences from different IP vendors, and then the chiplet itself will have its own licensing. So that whole business model has to be smoothed out,” he argued. Ending on a positive note, he said: “These are all solvable problems of course and will be solved, but those are important considerations.”

The end goal is to extend interoperability further, said Chakraborty. Heterogeneous integration would mean “using dies or even chiplets which are which are on different technology nodes. It could be . . CMOS integrating with photonic ICS for example,” he said. The ability to combine heterogeneous components from different vendors, supporting certain protocol stacks on which to build applications would necessitate interoperability, he concluded.

$35bn Synopsys takeover of Ansys conditionally approved by China regulator

Electronics Weekly

Electronics Weekly