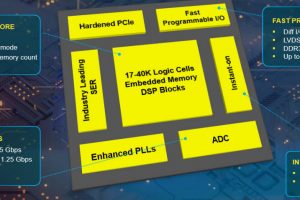

Lattice Semiconductor has released the second family of devices developed from its Nexus 28nm FDSoI platform, equipping them with fast PCI Express (PCIe) and Gigabit Ethernet interfaces for co-processing, signal bridging, and system control. Certus-NX FPGAs, as they will be known, are intended to be general purpose, aimed at applications from data processing in automated industrial equipment to system management ...

Programmable Logic and Asic

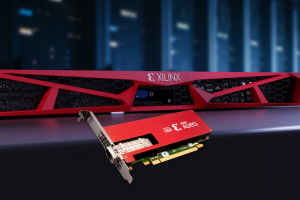

Xilinx targets live gaming audiences with Alveo appliances

Two real-time video appliances based on Xilinx‘s Alveo data centre accelerator cards target the computationally intense live broadcast applications, such as live gaming and Twitch audiences, as well as data centres. The video transcoding appliances are based on Xilinx’s Real-time Server architecture and reduce the bandwidth and matching costs for bit rates required by users or viewers. As audiences for live ...

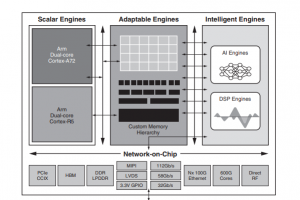

Xilinx announces addition to ACAP platform with Versal Premium

Xilinx has announced Versal Premium, the third series in its Versal ACAP portfolio. Versal is an adaptive compute acceleration platform (ACAP), a heterogeneous compute device with capabilities that the firm claims “far exceed” those of conventional silicon architectures. Added to the Premium series are 112Gbps pam4 transceivers, multi-hundred GBe and Interlaken connectivity, cryptography, and PCIe gen5 with built-in DMA, supporting ...

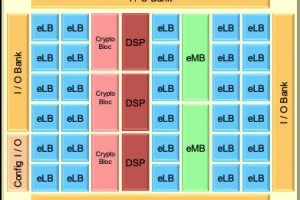

Embedded World: FPGA standard cells with crypto

Menta and Secure-IC are to add cryptographic features to FPGA intellectual property (IP). Under the agreement, announced at Embedded World in Nuremberg, the companies will deliver Menta eFPGAs incorporating cryptographic IP including AES and RSA from Secure-IC. “Security is fast becoming a defining feature of SoCs used in a variety of applications,” said Secure-IC CTO Sylvain Guilley. “The major challenge ...

Wind River, Xilinx tie up on ADAS

Wind River and Xilinx are co-developing an automated driving platform using Wind River’s automotive software and Xilinx’s ACAP chip. The collaboration will provide carmakers with a flexible compute platform for delivering connected and automated driving vehicles. The platform will deliver the foundation to enable a software architecture approach needed for autonomous driving applications, and make integration nearly plug and play. The ...

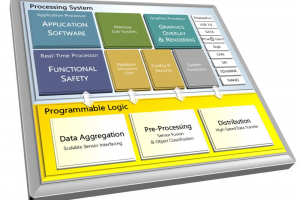

Xilinx adds to 16nm auto offering

Xilinx has expanded its automotive-qualified 16nm family with two new devices – the Xilinx Automotive (XA) Zynq UltraScale+ MPSoC 7EV and 11EG. These two new parts deliver the highest programmable capacity, performance and I/O capabilities enabling high-speed, data aggregation, pre-processing, and distribution (DAPD), as well as compute acceleration for L2+ to L4 advanced driver-assistance systems (ADAS) and autonomous driving (AD) applications. ...

Adaptable, flexible and open source: the wish list for young engineers

The working practices of today’s young engineers are very much on Victor Peng’s mind. The president and CEO of Xilinx explained why the company’s Vitis, the software platform announced at the Xilinx Developers’ Forum in San Jose, California. He conceded that the company has not normally been associated with open source products. Now it is offering Vitis. “The new generation ...

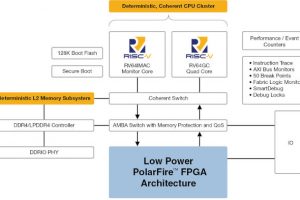

Risc-V day: Microchip adds Risc-V hard IP to PolarFire FPGAs

Microchip detailed an FPGA family with a quad core 64bit RISC-V processor alongside the programmable array. Called ‘PolarFire SoC’, the “architecture brings real-time deterministic asymmetric multiprocessing capability to Linux platforms in a multi-core coherent CPU cluster”, according to the firm, which worked with Risc-V specialist SiFive to create the devices. Real-time operation is included for safety-critical, system control and trusted ...

Xilinx puts new life into HTC and AI development

Xilinx embraces open source community and introduces the Vitis software platform for hardware and software development. At this year’s Xilinx Developers Forum, the company introduced the Vitis software platform, which tailors the hardware architecture to the software of algorithm code without intervention. President and CEO, Victor Peng, explained that the unified platform was developed to “empower software developers, with the ...

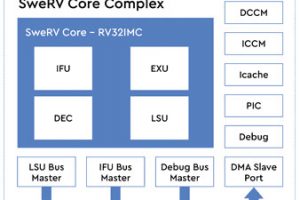

Risc-V day: Western Digital SweRV Core

Western Digital SweRV Core EHX1 is a 32-bit, 2-way superscalar, 9-stage pipeline core, originally designed to be used inside the firms data storage own products. Currently at version 1.1, it is open-sourced for the RISC-V community and, based on internal testing, is expected to deliver up to 4.9 CoreMarks/Mhz. “It offers capabilities for embedded devices supporting data-intensive edge applications, such ...

Electronics Weekly

Electronics Weekly