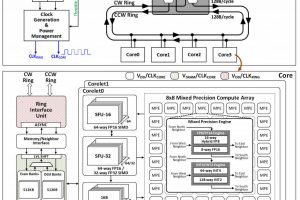

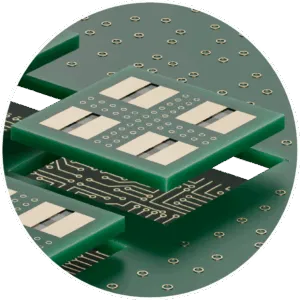

The Saras Tile, or STILE, enables power regulation from system board to package. Saras’ approach is for vertical power delivery to reduce parasitic losses. Stacking the power stage and passive components in line with the die shortens the power path and reduces parasitic losses. It also frees up board real estate by allowing the package to be placed on the back of the PCB. The vertical current flows directly from the PCB, through the package substrate and into the die.

In conventional power modules, passive components such as capacitors and inductors occupy more space than converter chips, reasoned Bart DeProspo, senior director of business development at Saras Micro Devices.

The company develops customised, integrated passive modules based on this 3D structure which provides centralised, vertical power delivery and dynamic responses times. It claimed that the power delivery enables AI chips, inference and timing applications, to operate with fewer voltage fluctuations and greater stability.

According to Saras, this approach “significantly reduces” the number of separate components needed while supporting “the most advanced high-power computing and AI applications”.

Freeing up real estate also enables higher levels of chiplet integration for the package to support the growing number of power rails being included within the package.

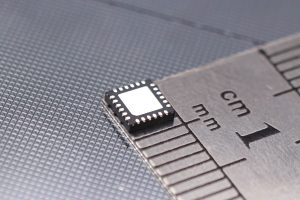

Package sizes range from 1.0mm x 1.0mm to 20mm x 20mm and are designed for integration into any organic substrate, regardless of silicon or package size, added the company.

Electronics Weekly

Electronics Weekly