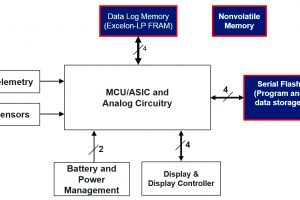

Some low-power strategies work for expanding memory storage in portable and implantable medical devices, says Shivendra Singh. The first challenge for system architects is to identify the right system on chip (SoC) or microcontroller to serve as the heart of the system. It must be capable of providing the desired performance while simultaneously reducing the overall system’s power budget. Peripheral ...

Memory

HotBackup for legacy systems

HotBackup is a solid state ‘live host’ backup for use in mission critical legacy systems

EW: Fujitsu 4Mbit FRAM reaches 54Mbyte/s operation

Fujitsu has launched a 4Mbit ferroelectric RAM (FRAM) with a quad SPI interface at Embedded World in Nuremberg. Called, MB85RQ4ML, with its four bi-directional I/O pins operating at 108MHz it can reach a data transfer rate of 54Mbyte/s. “In this respect, MB85RQ4ML is over four times as fast as our existing parallel 4Mbit FRAM device and even outperforms the 45ns parallel SRAM,” said ...

Solid-state drive has SATA III 6Gbit/s interface

Rutronik Embedded is offering a solid-state drive (SSD) from Transcend in a 2.5-inch form factor with integrated SLC NAND flash memory and a SATA III 6Gbit/s interface. The SSD570 has sequential read/write performance of up to 510Mbyte/s and 450Mbyte/s respectively. It comes with a built-in IPS function that assures more data volume being written into flash chips in the event ...

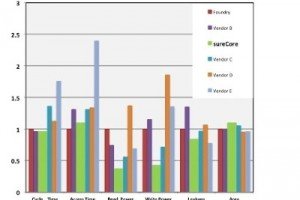

sureCore adds FDSOI memory compiler

sureCore, the Sheffield SRAM IP specialist, today announced the immediate availability of its 28nm FDSOI memory compiler. The compiler supports the company’s low power, single port SRAM IP and dual port SRAM IP for 28nm FDSOI process technology. It offers capacities up to 1Mbit with word lengths up to 288bits and supports 4, 8 and 16 Mux factors. According to the ...

Glasgow and Leeds researchers move towards racetrack memory

Researchers from the Universities of Glasgow and Leeds have developed materials for implementing racetrack memory. Racetrack memory uses lines of nanowires. Electricity passed through the wires creates ‘domain walls’ – spaces between the wires where information can be stored. Materials are still a key question for implementing the technology. The team from Glasgow and Leeds used electron microscopy to look ...

Toshiba gives NAND a serial interface for NOR replacement

Toshiba’s latest range of NAND flash memory chips have a serial interface. The advantage of the serial interface is that the devices can be controlled with just 6-pins, and this means they can be used as low-pin count SLC NAND flash memory. SLC NAND flash memory is now being used as a higher capacity alternative to NOR flash memory in some embedded ...

Micron legacy SDR/DDR modules live on at ATP

Micron Technology’s legacy DRAM modules (SDR/DDR) will be manufactured by ATP following a license agreement between the companies. Micron published EOL notices for these SDR and DDR DRAM modules in January 2015 with a Last Time Buy (LTB) in July 2015 and a Last Time Ship (LTS) in January 2016. Taiwan-based ATP will continue to manufacture these DRAM modules specifically for the ...

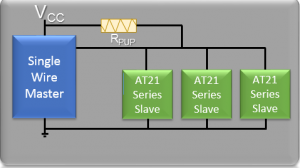

Atmel EEPROM needs just two pins, one wire

Atmel has designed a self-powered EEPROM which requires only two-pins—a data pin and ground pin – for operation. As the devices are self-powered, there is no need for a power source or Vcc pin, with a parasitic power scheme over the data pin. These single-wire EEPROMs have a specified power standby of 700nA, 200µA for write current, and 80µA for ...

SSD backs up legacy semiconductor manufacturing gear

Solid State Disks has launched an Ethernet-based back-up and restore capability for its family of Compact Flash (CF) SCSI-Flash solid-state drives for storage systems on legacy semiconductor manufacturing equipment.

Electronics Weekly

Electronics Weekly