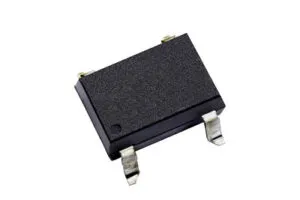

“The TOLL package is a 9pin, four-terminal package designed to facilitate the use of a Kelvin connection for its signal source terminal for the gate drive,” said the company. “The surface mounting capability of the TOLL package allows for smaller parasitic impedance, which leads to a reduction in switching losses.”

The parts are:

- TW027U65C 27mΩ typ (18Vg, 29A Id, 25°C), 40mΩ max

- TW048U65C 48mΩ typ (18Vg, 20A Id, 25°C), 71mΩ max

- TW083U65C 83mΩ typ (18Vg, 15A Id, 25°C), 124mΩ max.

The company picks out the middle part (TW048U65C) to demonstrate TOLL’s advantages over 3pin through-hole packaging: It “demonstrates a reduction in turn-on loss of approximately 55% and turn-off loss of around 25% compared to Toshiba’s equivalent product that uses the TO-247 package without a Kelvin connection”.

Improved Rds(on) stability with temperature is claimed with these SiC mosftets – part of Toshiba’s third generation.

In the same TW048U65C, typical on-resistance increases from 48mΩ to 53mΩ from 25°C to 150°C.

The gates are designed to be operated at 0V for ‘off’ (3.1μA typical leakage at 650V 25°C) and 18V for ‘on’, and will not be damaged across -10V to +25V. The gate threshold is between 3V and 5V.

Low Rds(on) x Qgd is claimed – the latter is typically 41nC (18Vg, 400Vd, 20A Id, 25°C).

Find the TW048U65C data sheet on this Toshiba web page

Infineon has some similar 650V SiC mosfets in TOLL packaging

Electronics Weekly

Electronics Weekly