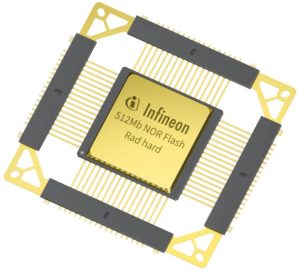

“The device offers a 133MHz quad serial peripheral interface and the highest density, radiation and single-event effects performance available in a QML-qualified non-volatile memory for use with space-grade FPGAs and microprocessors,” claimed the company.

To puts some numbers on these radiation claims, the figures are 300 krad(Si) total ionising dose (TID), >80MeV.cm2/mg single event latch-up (linear energy transfer at 125°C), <2.77e-5 err/dev.day single event functional interrupt, and immunity from single event upset (SEE).

“The device offers the highest density TID/SEE performance combination for space FPGA boot code solutions, and the QML-V/P with DLAM certification meets the most stringent industry qualifications,” according to Infineon. It “is based on Infineon’s SONOS [silicon-oxide nitride-oxide-silicon) charge gate trap technology with endurance of up to 10,000 programme-erase cycles and up to 10 years of data retention. A ceramic QFP QML-V package occupies 1 x 1in board area, and a smaller footprint plastic TQFP QML-P 0.5 x 0.8in is available.”

The parts, as far as Electronics Weekly can determine, are:

| Qualification | Package | |

| CYRS17B512-133AZMB | Infineon in-house | 100pad plastic TQFP |

| CYPT… | For prototypes | |

| 5962F2122201PXE | DLAM QML-P | |

| CYRS17B512-133UZMB | Infineon in-house | 68pad ceramic CQFP |

| CYPT… | For prototypes | |

| 5962F2122202VYC | DLAM QML-V |

This table was has been compiled from several Infineon documents and may contain errors – clarification has been requested.

Operation is from 3 or 3.3V supply (2.97 V to 3.63 V), and IO can be at the same voltage or at a nominal 1.8V (1.71 to 1.89V). Operation is also over –55 to +125°C.

The memory was jointly developed with Micro-RDC, and part funded by the US Air Force Research Laboratory

A typical use case for this device includes configuration image storage for space-grade FPGAs and standalone boot code storage for space grade multi-core processors.

Electronics Weekly

Electronics Weekly