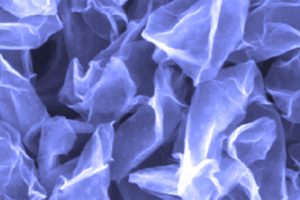

Continuing the industry’s love affair with lithium for batteries, researchers have found a way to avoid dendrites which grow on as the battery charges and discharges and which can degrade performance. Building on work began by Jiaxing Huang, professor of materials science and engineering at Northwestern University’s McCormick School of Engineering, Jiayan Luo, professor of chemical engineering at Tianjin University ...

Process

Clock-speed slowdown continues

It’s no secret that the clock speeds of processors have hit a glass ceiling. But until the latest iteration of the International Technology Roadmap for Semiconductors, we still expected them to increase by close to 10 per cent a year. Not anymore. The slow rise has been replaced by a crawl that acknowledges the need to keep both cost and ...

ITRS 2011 published

The 2011 International Technology Roadmap for Semiconductors (ITRS), finalised late last year, has been publicly released. The roadmap looks at the problems facing the chipmaking industry from now until 2026 and includes some updates that focus on low-power design. The slides prepared by Andrew Kahng on design, for example, show how expectations on power have changed – and in a quite ...

Anneal from the back for better leakage

One of the biggest contributors to leakage power in advanced processes is variability and the need to use guard banding to avoid having a chip fail because critical paths wind up in ‘cold’ high-delay parts of the die.

Circuit choices encroach on IEDM

The emphasis of the IEDM conference is shifting away from peak speed to more of a tradeoff between power and performance, with several papers reflecting the need to move away from traditional transistor metrics such as current drive.

The metal gate’s hidden problem

Process variability does not immediately sound as though it has an impact on low-power design, but it has several insidious consequences. And it’s gradually getting to be more of a problem. Variability causes higher power consumption because of the way it can shift the threshold voltage, which can make transistors a lot leakier than they should be. Typically, the leakage ...

There can be only one…or two

Mainstream CMOS process development is a little like Highlander: there can be only one. It matters which choices other chipmakers make because they will control how quickly the industry as a whole can get down the yield learning curve – and how much the end product costs. It is possible to use more exotic processes but these really only succeed ...

Low power at DAC

The Design Automation Conference, which returns to San Diego this year, is now less than a month away and has put together a programme that includes coverage of low-power design issues. Tuesday 7 June has a panel that attempts to work out who in the design chain can make the biggest savings, from device physicists to systems and software engineers. ...

More options for low-power processes

In days of yore, one process used to fit them all. Then CMOS processes split into high-power (HP) and low-power (LP) process options. As 3D transistors such as the finFETs that Intel will deploy at 22nm become more common, we can expect even more options to appear.

Panasonic’s first gate-first parts emerge

When Panasonic said it would ship its first parts based on a 32nm high-k, metal-gate process by last October, technical analyst firm Dick James of Chipworks was confident the company would hit its deadline and beat many of the other companies planning HKMG.

Electronics Weekly

Electronics Weekly