A single structure built in the metal layers of an IC can implement both machine learning and analogue AI inferencing, according to a French team led by Grenoble lab CEA-Leti – and the CMOS below can also be used for processing. Made between two metal interconnect layers, the structure has four layers: TiN at the bottom, Si-doped HfO2, a Ti ...

DAC

Stay updated on the latest from the Design Automation Conference (DAC) — the leading event for professionals in electronic design automation, silicon design, IP, embedded systems, and software. DAC brings together researchers, engineers, and industry leaders to explore innovations across chip design, AI/ML acceleration, system architecture, verification, and more. With a rich programme of technical papers, keynotes, panels, and exhibits, DAC serves as a critical hub for advancing the future of semiconductor and system design. Discover insights, breakthroughs, and product announcements from one of the most influential conferences in the semiconductor ecosystem.

The chiplet future could be harmonious

There is a general consensus and belief that chiplets are the future, said Abhijeet Chakraborty, VP engineering, Synopsys. There are, however, no illusions about some of the challenges or obstacles that have to be addressed, he added. The first of these is interoperability and standards. Access to chiplets is essential to design any complex, large system, Chakraborty told Electronics Weekly ...

Working group to tackle interoperability for system-of-systems simulation

A new working group has been announced to establish cross-industry collaboration to improve the interoperability of product and environment simulation, models, and components using existing and new open standards. Accellera Systems Initiative announced the Federated Simulation Standard (FSS) working group (WG). The charter of the new working group is chaired by NXP’s Martin Barnasconi,with Qualcomm’s Mark Burton as vice chair. ...

Will the Chips Act finance innovation?

How does the (US) Chips Act affect innovation? This question was posed at DAC and the expert panel agreed that there is no lack of engineering talent but how to corral it to the right areas is proving more complex. Saverio Fazzari, senior lead engineer at management consultancy Booz Allen Hamilton. Workforce development, expressed his hopes for the cash injections. ...

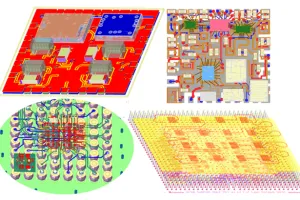

Keysight and Synopsys employ AI for RF design migration

Keysight has combined it Electromagnetic Simulator with Synopsys’ AI-powered RF design migration flow for an integrated design flow to migrate from TSMC’s N6RF+ to N4P process technology. The migration workflow builds on the foundry’s Analog Design Migration (ADM) methodology to streamline the redesign of passive devices and design components to the advanced RF process rules. The collaborative migration workflow leverages ...

Atlas suite marks MIPS’ drive to co-design

For physical AI at the edge, MIPS has introduced the Atlas Explorer portfolio. The company explained that it allows designers cycle-accurate repeatability of their workload onto a MIPS processor. It provides access to platform IP ahead of silicon availability for evaluation to enable pre-production RTL and for teams to develop optimised hardware and concepts such as digital twins to gain ...

Siemens applies AI across chip and PCB design portfolio

DAC 2025: There was a lot of talk about AI at this year’s DAC but one of the most significant was that Siemens Digital Industries Software has added generative and agentic AI capabilities across its EDA portfolio. The EDA AI system applies across all semiconductor and PCB design suites, including Questra, Tessent, Xpedition, Veloce, Catapult, Calibre, Aprisa and Solido. “It ...

What caught your eye? (3D IC design, Robotaxi, Accelerometers, SOOP)

This week we're talking about 2.5D and 3D IC design, the robotaxi market, a rush of accelerometers, and sampling broadband satcom signals for navigation purposes...

Translation tool tackles optimisation in large SoCs

Designers looking to optimise PPA (power, performance, area) are finding that optimisation engines can render original programmatic timing constraints unusable in their original form. At DAC 2025, Ausdia introduced Timevision OneSource which automatically generates a new version of block-level constraints after optimisation engines have worked on hierarchies, duplicate elements and performed advanced transformation. Such optimisations can save two weeks of ...

DAC 2026

DAC moves to Long Beach, southern California for 2026. The exhibition and conference covers chips to systems with education, exhibits, training and networking opportunities for designers, researchers, tool developers and vendors. It is of interest to system designers and architects, logic and circuit designers, validation engineers, CAD managers, senior managers and executives, and researchers and academicians from leading universities. The ...

Electronics Weekly

Electronics Weekly