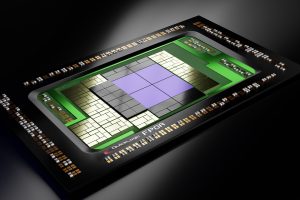

In Las Vegas, Cadence announced that Arm, Arteris, eMemory, M31 Technology, Silicon Creations and Trilinear Technologies are IP partners for the Physical AI chiplet platform and chiplet framework. The ecosystem also includes silicon analytics partner proteanTecs. A silicon prototype demonstration will be built with pre-integrated partner IP on the Samsung Foundry SF5A process.

Arm’s Zena compute subsystem will be used with other IP. According to Cadence, the platform will accommodate edge AI requirements for automotive design, robotics and drones, as well as standards-based I/O and memory chiplets for data centre, cloud and HPC applications.

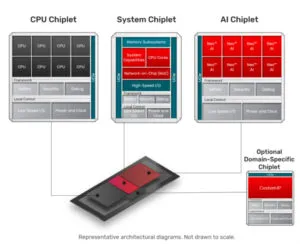

The aim of the alliance is to reduce engineering complexities, offer customers a low-risk path to advanced chiplet adoption and pave the way for smarter, safer and more efficient systems, said the company. Multi-die and chiplet-based architectures can provide flexibility through customisation and configurability but design can be long and complex.

Spec-driven automation, using pre-integrated and pre-validated IP from Cadence and partners, accelerates the generation of chiplet framework architectures. Complete with chiplet management, security, and safety features, supported by software.

The generated EDA tool flow enables seamless simulation with Cadence’s Xcelium logic simulator and emulation with Palladium® Z3 Enterprise emulation platform. The physical design flow uses real-time feedback for place-and-route cycles.

The chiplet architectures are standards-compliant, including to the Arm Chiplet System Architecture and future OCP Foundational Chiplet System Architecture. For industry-standard die-to-die connectivity, there is Cadence’s Universal Chiplet Interconnect Express (UCIe) IP. Other IP enables LPDDR6/5X, DDR5-MRDIMM, PCI Express (PCIe®) 7.0, and HBM4 interface integration.

Electronics Weekly

Electronics Weekly