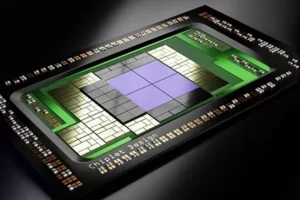

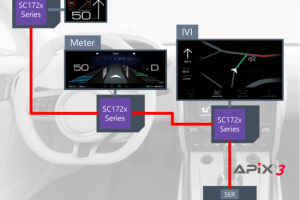

As traditional monolithic SoC designs face physical and economic limits – reticle size constraints, yield challenges, and thermal bottlenecks – the industry is turning toward chiplet-based design, where designers can integrate their core features and interface functionalities, provided as chiplets, into a packaged device to improve performance, cost, and accelerate time-to-market.

While chiplet technology opens exciting possibilities for modular designs and scalability, many current solutions are derived from fixed-function ASSPs, limiting flexibility and customization.

Flexlets overcome this by offering a configurable library of chiplet designs at the RTL level. Unlike traditional approaches, Flexlets empower customers to tailor performance to their unique application needs – whether in high-performance computing, advanced networking, or next-generation automotive systems.

Unlike competitors who are limited to their own ecosystem, Flexlets from Socionext enable customers to co-design differentiated features by integrating best-in-class IP from any vendor. This flexibility is a game-changer for companies aiming to deliver state-of-the-art designs with optimised power, performance, and area (PPA) in a competitive market.

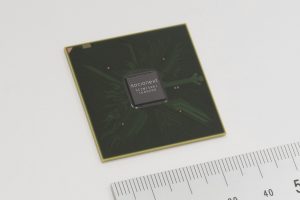

Socionext will launch a portfolio of Flexlets, each integrating security, debug features, and optimised interfaces. Customers have the option to customise their designs at the RTL level to meet specific application requirements. Engineering samples of the initial Flexlet base designs, including Known Good Die (KGD), are currently in development. Socionext will initiate its first customer design this year and broaden design engagements beginning in Q2 calendar year 2026.

• Memory Expansion Flexlets

Scalable memory solutions with support for the latest DDR/LPDDR standards connected to either

UCIe-S or UALink• Ethernet Controller Flexlets

Robust and high-performance networking connectivity via 224G/UE bridged to UCIe 2.0

• PCIe Controller Flexlets

Seamless integration to PCIe ecosystem by bridging PCIe Gen7 128G PHY to UCIe 2.0 with configurable lanes

• Hybrid PCIe + Ethernet Controller Flexlets

A versatile range of I/O capabilities, bridging high-speed SerDes (224G/UE) to UCIe 2.0

All Flexlets support 2.5D/3D advanced packaging, including CoWoS, SoW-X, EMIB, and 3D stacking, leading-edge process nodes (5, 3, 2nm), and industry standards, including UCIe, UALink, PCIe Gen7, and Ultra

Ethernet – enabling robust interoperability across multi-vendor ecosystems.

Socionext’s packaging capabilities rival those of the largest chipmakers. With successful tapeouts in 2nm and 3DIC test vehicles, the company offers real-world proof of engineering excellence, including support of multiple – 64 to 128 – instances of high-speed 224G SerDes in a Flexlet. In a market still lacking standardized design rule checks for large chiplet-based packages, Socionext provides the credibility and capability customers need to innovate with confidence.

Socionext will redefine flexible chiplet-based architectures to meet the demands of today’s most advanced systems applications. Flexlets deliver a scalable, modular foundation for next-generation silicon design, built for adaptability, performance, and innovation.

Electronics Weekly

Electronics Weekly