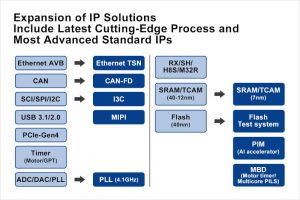

Renesas Electronics Corporation has announced expanded access to its IP license portfolio. Customers will gain access to IPs such as 7nm SRAM and TCAM, and standard Ethernet time-sensitive networking. Renesas is working on providing a system IP which includes processing-in-memory. These are suggested to help customers with projects like next-gen AI chips or ASICs for 5G networks. Customers developing custom ...

EDA and IP

SiFive adds Risc-V micro-instruction cache for slow memories

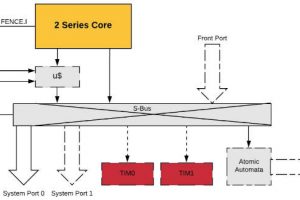

SiFive has added a ‘micro instruction cache’ option to its Risc-V e2 core – the smallest of its Risc-V intellectual property offerings. Introduced in release 19.05, the micro instruction cache (see μ$ for cache in diagram) sits between the instruction fetch port and the memory system, and offers a speed-up in execution when operating from slower memories such as NVM ...

Arm TechCon: Autonomous car consortium formed

The Autonomous Vehicle Computing Consortium (AVCC), launched at Arm TechCon in San Jose, brings together Arm, Bosch, Continental, DENSO, General Motors, NVIDIA, NXP Semiconductors and Toyota to help solve some of the challenges to deploy self-driving vehicles. The first is to develop a set of recommendations of a system architecture and a computing platform that reconciles the performance requirements of autonomous ...

Arm TechCon: Custom Instructions launched

Announced at Arm TechConArm, Custom Instructions are a new feature for the Armv8-M architecture.

Arm TechCon: UltraSoC hardware cybersecurity IP

UltraSoC has announced hardware-based cybersecurity intellectual property products for SoCs at Arm TechCon in San Jose. According to Cambridge-based UltraSoC, they can be used to detect, block and record cyber-attacks, as well as preventing their propagation, in vehicles, factory robots and consumer devices, amongst other applications. “The first product in the range, the UltraSoC Bus Sentinel, allows SoC designers to control ...

Risc-V day: Andes offers IP cores, accelerators, tools, and even a free core

Taiwanese IP provider Andes Technology is offering RISC-V cores, acceleration hardware and development tools. Amongst planned cores is a free one. “With ‘Fast start’ into Risc-V, we will not only introduce our free starter, commercial grade core but also show which other options available, ranging from an ultra-low power MCU over a low power medium-sized Core up to Linux-capable multi-core processors ...

Adaptable, flexible and open source: the wish list for young engineers

The working practices of today’s young engineers are very much on Victor Peng’s mind. The president and CEO of Xilinx explained why the company’s Vitis, the software platform announced at the Xilinx Developers’ Forum in San Jose, California. He conceded that the company has not normally been associated with open source products. Now it is offering Vitis. “The new generation ...

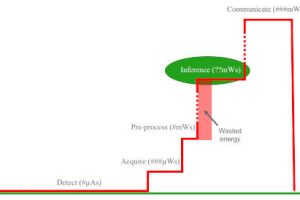

Risc-V day: Greenwaves’ pushes AI to the very edge of IoT

GAP 8 is an ultra-low-power Risc-V AI processor from Grenoble-based GreenWaves, aimed at inferencing (executing already-trained neural networks) inside battery-operated IoT sensors. “Battery-operated sensors have, until now, been restricted to simple data sources such as temperature and humidity,” according to the firm. “But there is increasing interest in processing richer data sources such as images, sounds, and vibrations. These applications require ...

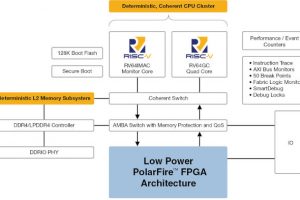

Risc-V day: Microchip adds Risc-V hard IP to PolarFire FPGAs

Microchip detailed an FPGA family with a quad core 64bit RISC-V processor alongside the programmable array. Called ‘PolarFire SoC’, the “architecture brings real-time deterministic asymmetric multiprocessing capability to Linux platforms in a multi-core coherent CPU cluster”, according to the firm, which worked with Risc-V specialist SiFive to create the devices. Real-time operation is included for safety-critical, system control and trusted ...

Xilinx puts new life into HTC and AI development

Xilinx embraces open source community and introduces the Vitis software platform for hardware and software development. At this year’s Xilinx Developers Forum, the company introduced the Vitis software platform, which tailors the hardware architecture to the software of algorithm code without intervention. President and CEO, Victor Peng, explained that the unified platform was developed to “empower software developers, with the ...

Electronics Weekly

Electronics Weekly