It is running FD-SOI wafers for RF, NVmemories and PMICs.

The open-access line is accessible primarily, but not exclusively, to European startups, SMEs, industrial groups, and research organizations seeking to prototype, qualify, and de-risk advanced semiconductor technologies before industrial deployment.

“The technologies developed within FAMES are intended to support future generations of sub-10 nm FD-SOI chips, enabling high-performance and low-power components for Europe,” says CEA-Leti CTO Jean-René Lèquepeys, “scaling down the FD-SOI technology to 10 and 7nm will bring significant chip performance improvements compared to current nodes, in density, power consumption, speed and radio-frequency behaviour.”

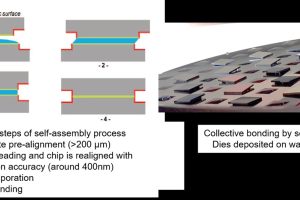

CEA-Leti recently demonstrated fully functional 2.5 V SOI CMOS devices fabricated at a thermal budget of 400 °C.

Achieving performance comparable to conventional high-temperature CMOS, the work removes a key barrier to large-scale 3D sequential integration and enables dense multi-tier chip architectures compatible with advanced back-end processes—one of the central technical objectives of FAMES.

Electronics Weekly

Electronics Weekly