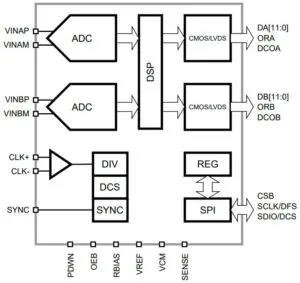

“The integration of a DSP brings several functions on-chip, including decimation, digital down-conversion, interleaving and IQ-mismatch correction – these would traditionally be undertaken by an FPGA,” according to the company.

The dual-channel, 12-bit, 170Msample/s ADC version is called SD1146.

“The device uses a multistage pipeline architecture to achieve high signal-to-noise ratio and linearity, over wide input signal bandwidth,” claimed Silanna.

Simplified DSP block diagram

It has a 2Vp-p nominal input with claimed signal-to-noise of 70.8dBfs, 88dBc SFDR (spurious free dynamic range) and -151.3dBfs/Hz input-noise – all with 70.2MHz on the input, sampling at 170Msample/s. (‘fs’ here is ‘full-scale’).

The ADCs can be operated individually, or as I and Q channels for the same signal.

They have a sample-and-hold at their front ends and are fully differential for noise rejection.

“The input stage behaves as a switched-capacitor network, presenting itself to the driving circuit as a combination of a switch and a sampling capacitor,” said Silanna. “The capacitor is reset prior to each conversion cycle, effectively eliminating non-linear memory effects commonly observed in some pipelined ADC architectures.”

Inputs are expected to be AC-coupled via capacitors and a voltage output is provided with which to set input DC values. An internal 1.02-1.07V reference is included for conversion.

Calibration is automatic at switch-on, and can be initiated manually during operation. There is also a background calibration mode.

Control is via a three-wire SPI-compatible bus and the IC can be set to operate its data output to either CMOS or LVDS (ANSI-644) levels, and in offset binary, twos complement or Gray code format.

An external clock is required at up to 1GHz, in either differential or single-ended form. This is processed by an internal divider with integral ratios from 1 to 8.

Analogue and digital supplies of 1.8V are needed, and power consumption is typically 492.4mW at 170Msample/s. Operation is over -40°C to +85°C.

ADC versions of 14- and 16-bit are under development, with sample rates from 5Msample/s to 250Msample/s.

Find the SD1146 datasheet on this Silanna web page, and find out about the company’s earlier DSP-less ADCs here

A Gemini 3-generated image of the Silanna SD1146 block diagram above:

Electronics Weekly

Electronics Weekly