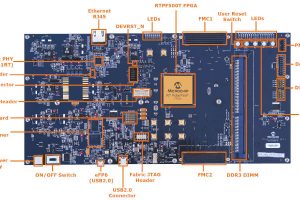

The FPGAs enable I/O expansion, sensor processing and control, and board management and are suitable for devices and sensors connected at the edge, including industrial automation, networking, robotics, wireless applications and industrial IoT. They are also suitable for data centre interconnect, IIoT gateways and medical equipment, including imaging equipment.

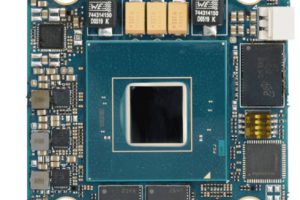

Densities for the Spartan UltraScale+ FPGAs range from 11k to 218k logic cells and up to 572 I/Os. They are designed for large amounts of data and have an integrated memory controller for LPDDR4X/5 supporting up to 4266Mbps on a 32-bit interface. Mouser said this saves up to 15k logic cells contributing to reducing the power budget.

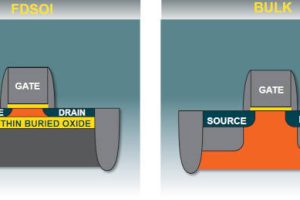

Other connectivity options are PCIe Gen4 and MIPI D-PHY. Mouser said that 16nm FinFET and power efficiency through hardened DDR and PCIe contribute up to 30% power reduction.

The FPGAs can be interfaced with 1.2V-3.3V I/O or 16.3Gbps transceivers. Security features include hard IP for post-quantum cryptography and NIST-approved algorithms. This combination allows secure device configuration and provides user access to dedicated cryptographic resources, including a true random number generator (TRNG), physical unclonable function (PUF) and secure hashing.

The FPGAs are supported by AMD Vivado design tools. AMD also provides Artix UltraScale+, Artix 7, Spartan 7 and Spartan 6 FPGAs.

Electronics Weekly

Electronics Weekly