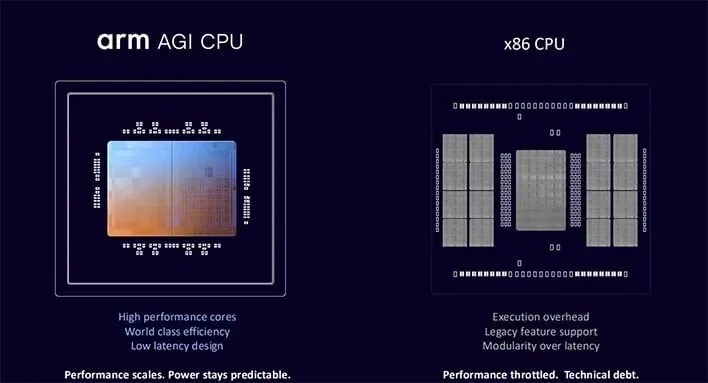

The processor, designated Arm AGI CPU, is targeted at agentic AI infrastructure. Arm says it delivers more than two-times performance per rack compared with x86 platforms.

“Today marks the next phase of the Arm compute platform and a defining moment for our company,” says CEO Rene Haas. “With the expansion into delivering production silicon with our Arm AGI CPU, we are giving partners more choices.”

Arm expects that selling proprietary discrete chips will boost annual revenues five-fold in five years to $25bn. By that time IP sales are expected to be $10bn.

The chip has a 300W TDP. Of its Neoverse V3 cores, 136 are clocked at up to 3.7GHz (3.2GHz base), on two die fabbed on TSMC’s 3nm process. It has 2MB of L2 cache per core along with 128MB of shared system-level cache.

Agent-driven applications in datacentres could need more than four-times the current CPU capacity per GW within the same power envelope requiring “a simplified architecture built without the overhead and complexity of x86 processors”, says Arm.

The Arm AGI CPU delivers:

- Performance: Up to 136 Arm Neoverse V3 cores per CPU, delivering leading performance per core, SoC, blade and rack, with 6GB/s memory bandwidth per core at sub-100ns latency.

- Scale: 300-watt TDP with a dedicated core per program thread enables deterministic performance under sustained load, eliminating throttling and idle threads.

- Efficiency: Supports high-density 1U server chassis that supports air-cooled deployments with up to 8,160 cores per rack and liquid-cooled systems delivering 45,000+ cores per rack.

Arm designed the chip with Meta and partners including Cerebras, Cloudflare, F5, OpenAI, Positron, Rebellions, SAP and SK Telecom.

These customers will deploy the Arm AGI CPU for key agentic CPU use-cases including accelerator management, control plane processing and cloud and enterprise-based API, task and application hosting.

OEM/ODM partners are ASRock Rack, oEM/ODMLenovo, Quanta Computer, and Supermicro, with early systems available now and broader availability expected in the second half of the year.

Electronics Weekly

Electronics Weekly

The CPU must reside on the same silicon as NPU and GPU to be efficient. Few tasks can be handled by one alone.