Cadence has announced what it claims is “industry’s first comprehensive high-capacity 3D IC platform that integrates 3D design planning, implementation and system analysis in a single unified cockpit.” It is called ‘Integrity 3D-IC’ and is said underpin the company’s third-generation 3D IC solution, providing power, performance and area for individual chiplets through integrated thermal, power and static timing analysis capabilities. ...

EDA and IP

Security software protects at pre-silicon stage

Pre-silicon security verification during the chip design stage can avoid time-consuming analysis and correction of security vulnerabilities for a manufactured device. It can also avoid potential re-spins and production delays, says FortifyIQ. The company has developed two software suites which simulate some of the ‘popular’ methods of cyberattack. SideChannel Studio simulates side-channel attacks whereby cyber criminals measure physical characteristics, such as power ...

Power integrity software provides full chip analysis

Believed to be the first electromigration/voltage drop (EM/IR) tool for both analogue and digital methodologies, mPower has been released by Siemens Digital Industries. The tool marks Siemens’ entry into the IC power analysis market, capable of power integrity analysis for analogue, digital and mixed-signal IC designs. It is also scalable and uses industry standard inputs and interfaces. Power integrity analysis ...

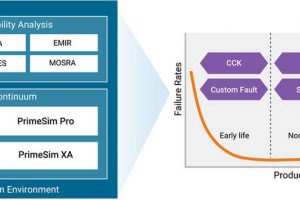

Synopsys unifies its reliability analysis workflow

Synopsys has unified the workflow through its existing reliability analysis tools for analogue, mixed-signal and custom IC designs – integrating them into its PrimeWave design environment, along with PrimeSim Continuum that announced in April. The unified workflow is to be called PrimeSim Reliability Analysism and is an umbrella for its CKK, Custom Fault, AVA, SPRES, EMIR and MOSRA tools (see table ...

C++ synthesis suite for PolarFire FPGA algorithm development

Microchip has released a C++ algorithm high-level synthesis design workflow for its PolarFire FPGAs. “A large majority of edge compute, computer vision and industrial control algorithms are developed natively in C++ by developers with little or no knowledge of underlying FPGA hardware,” according to the company. Called SmartHLS, the tool allows C++ algorithms to be directly translated to FPGA-optimised RTL ...

A core challenge

A common verification methodology available to both RISC-V core providers and SoC teams integrating these cores is required, argues Nicolae Tusinschi of Siemens. Modern processor designs present some of the toughest hardware verification challenges. Verification is particularly challenging for RISC-V processor core designs, with many providers and many variations of implementation. The flexibility that RISC-V provides makes it especially difficult ...

Intrinsic ID joins DARPA Toolbox Initiative

Intrinsic ID, Physical Unclonable Function (PUF) security IP specialist, has had its ID QuiddiKey hardware IP and Apollo FPGA IP adopted for the DARPA Toolbox Initiative, which provides DARPA researchers open licensing opportunities with commercial technology vendors. QuiddiKey IP can be applied to almost any chip – from MCUs to high-performance SoCs, to secure the products with internally generated, device-unique ...

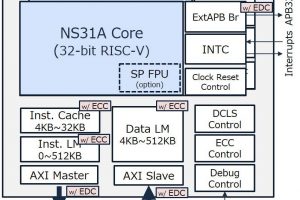

Functional safety development support for automotive Risc-V

IAR Systems extended coverage of the functional safety version of its Embedded Workbench software tool chain to the 32-bit Risc-V core of Nsitexe, a subsidiary of automotive parts maker Denso. “Functional safety is a constant growing requirement for embedded systems, with automotive applications, industrial automation and medical devices as three of the major driving forces,” according to IAR Systems. “With ...

Realtek licences Imagination GPU for DTV

Realtek has licensed Imagination Technologies’ IMG B-Series BXE-4-32 GPU for a system-on-chip aimed at mass market digital television. BXE-4-32 was selected, said Imagination, for area efficiency while processing four pixels per clock, plus its multi-core capability and cache configurability. BXE also features Imagination’s IMGIC multiple-quality-level real-time image compression technology that “enables DTV platforms with a BXE-4-32 GPU to configure and optimise ...

Andes certifies Risc-V SIMD and DSP reference models

Risc-V core design house Andes Technology has certified reference models for its cores with ‘P’ extensions from Imperas. Cores carrying the P designation have SIMD and DSP extensions to the instruction set for data processing and real-time operation. “The RISC-V International P Extension Task Group is in the final stages of submitting the specification to the official ratification process, which ...

Electronics Weekly

Electronics Weekly