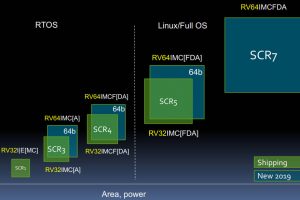

Syntacore has been developing processor core IP based around the Risc-V instruction set for four years

EDA and IP

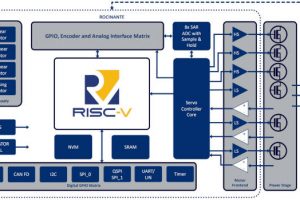

Risc-V day: Trinamic Rocinante motor drive

Trinamic described why it had chosen Risc-V over other processor architectures for Rocinante

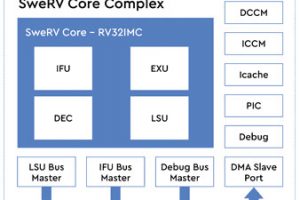

Risc-V day: Western Digital SweRV Core

Western Digital SweRV Core EHX1 is a 32-bit, 2-way superscalar, 9-stage pipeline core, originally designed to be used inside the firms data storage own products. Currently at version 1.1, it is open-sourced for the RISC-V community and, based on internal testing, is expected to deliver up to 4.9 CoreMarks/Mhz. “It offers capabilities for embedded devices supporting data-intensive edge applications, such ...

First silicon for Flex Logix validation chip

Flex Logix says it has received working first silicon of its validation chip for the EFLX 4K eFPGA IP

Moortec In-Chip Monitoring IP on TSMC 5nm

Moortec has availability of its latest In-Chip Monitoring IP Subsystem on TSMC’s N5 and N5P process technologies. A global acceleration in cutting-edge technologies including 5G, Artificial Intelligence (AI), Machine Learning and Data Centre High Performance Computing is fuelling the demand on TSMC’s 5nm FinFET process technology. Such devices are required to operate at the highest level in terms of power, ...

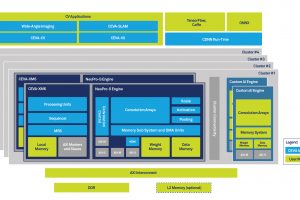

CEVA adds system awareness to AI inference processor

The company introduced the second-generation NeuPro architecture for edge devices. NeuPro-S processors address the need to scale up its NeuPro architecture to work in heterogeneous systems, explained Yair Siegel, director of segment marketing. There are three processors available, targeting the mobile, home and automotive markets, all have safety standards enabled, added Siegel. Launched at this week’s AutoSens in Brussels, Belgium ...

Sir Hossein Yassaie joins Agile Analog

Sir Hossein Yassaie, founder and CEO of Imagination, has become a non-exec at Agile Analog, the Cambridge analogue EDA startup. Agile Analog is set on automating the design and delivery of analogue IP. Using its AI-driven approach, Agile Analog has automated the traditionally manual design process and is creating analogue IP that aims to be more customisable, more reliable and ...

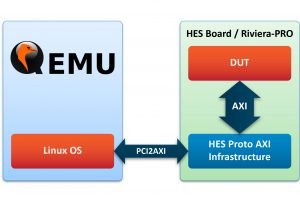

Aldec enhances verification and validation tool

Aldec improves its HES Proto-AXI software to provide greater support hardware verification and software validation.

Imagination diversifies into design and verification services

Imagination is expanding its business with a tailored consultancy, hosting and deployment service for design and verification, called IMG Edge. IMG Edge is targeted at reducing time to market and total cost of ownership and includes an extensive get-to-market support package to address the complex and expensive challenges involved when bringing compute-focused SoCs to market. Providing access to Imagination’s data ...

More on: MIT’s carbon nanotube RISC-V CPU

Last week MIT announced a CPU made from carbon nano-tube (CNT) mosfets using standard CMOS fab equipment and only the materials and processes found within commercial CMOS fabs. Electronics Weekly has delved inside to see how it works. In essence, the CNT logic is CMOS, as the researchers have found a way to create p-channel CNT mosfets and n-channel mosfets with ...

Electronics Weekly

Electronics Weekly