JEDEC has officially updated its LPDDR5/5X Serial Presence Detect (SPD) Contents standard, adding support for calculating recovery time when switching operating modes, with JESD406-5D. Bill Gervasi of Monolithic Power Systems, and chair of the JEDEC SPD Task Group, commented: “Reducing power consumption has become imperative for computing systems as the use of AI and other demanding applications accelerate. The updates to ...

Memory

The latest Electronics Weekly product news on memory technology (such as Flash, MRAM, SSD, NAND, F-RAM, DRAM, etc).

Embedded World Video: Weebit Nano on why we need ReRAM

At Embedded World 2026 we caught up with Coby Hanoch, CEO of Weebit Nano, as part of our promotional coverage for the event. He explains why we need a new kind of NVM (Non-Volatile Memory), which big companies are using, and how it enables new embedded applications in AI, compute in memory and neuromorphic. Thank you to Coby for his ...

Micron in volume production of HBM4 for Vera Rubin

Micron has begun volume shipment of its HBM4 36GB 12H designed for NVIDIA Vera Rubin and capable of over 11 Gb/s pin speeds, enabling a bandwidth greater than 2.8 TB/s. Micron is also sampling HBM4 48GB 16H which stacks 16 HBM die. “The next era of AI will be defined by tightly integrated platforms developed through joint engineering innovations – ...

Memory shortage to last 4-5 years says SK boss

The memory shortage could last another four to five years, says the chairman of SK Group, Chey Tae-won. The supply of base wafers is lagging demand by more than 20%, says Chey. “AI actually wants to have a lot of HBM, and once you make the HBM…we have to use a lot of wafers,” said Chey, “So we need some ...

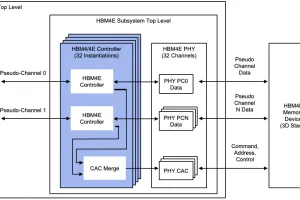

Rambus announces HBM4E controller IP

Rambus has launched HBM4E Memory Controller IP. The HBM4E Controller supports operation up to 16 Gbps per pin providing a throughput of 4.1 Terabytes per second (TB/s) to each memory device. For an AI accelerator with eight attached HBM4E devices, this translates to over 32 TB/s of memory bandwidth for next-generation AI workloads. The Rambus HBM4E Controller IP can be ...

Jedec updates Universal Flash Storage for faster edge AI

Jedec has officially updated the Universal Flash Storage (UFS) standard with UFS 5.0. It aims to increase storage performance and efficiency for edge device AI applications. The aim is improved performance through faster data access. For example, UFS 5.0 enables sequential read and write speeds of up to 10.8GB/s. Note, however, the changes maintain compatibility with UFS 4.x hardware. The ...

Kioxia sampling UFS 5.0 NAND

Kioxia is sampling UFS 5.0 NAND which is currently being standardised by JEDEC. UFS 5.0 is designed to meet the performance requirements of smartphones equipped with on-device AI functions. It uses MIPI M-PHY version 6.0 for the physical layer and UniPro version 3.0 for the protocol. M-PHY version 6.0 introduces the new HS-GEAR6 mode, theoretically supporting an interface speed of ...

ZAM challenge to HBM

Prototypes of Z-Angle Memory (ZAM) are slated for 2027, says Intel, with mass production scheduled for 2030. ZAM, a stacked DRAM alternative to HBM with a claimed 40-50% power advantage and 2x-3x density advantage over HBM, is the product of a jv between Softbank, Tokyo University and Intel called Saimemory which was later joined by Fujitsu. The initial technology came ...

Kioxia highlights 1TB quadruple-level cell for UFS 4.1

Kioxia is sampling UFS (Universal Flash Storage) 4.1 embedded memory devices with 4-bit-per-cell, quadruple-level cell (QLC) technology. The new devices feature the company’s 8th generation BiCS FLASH 3D flash memory technology. It highlights this as introducing CMOS directly Bonded to Array (CBA) technology. There is also an integrated controller in a JEDEC-standard package. Kioxia says the QLC UFS memory design ...

HBM4 set back a quarter for re-design

HBM4 mass production has been put back to the end of Q1 at the earliest, TrendForce, after Nvidia increased the spec for the pin speed for its Rubin platform to over 11Gbps requiring a redesign by Hynix, Samsung and Micron. All three companies are said to have submitted re-designed samples. Samsung is said to be utilising a more advanced process ...

Electronics Weekly

Electronics Weekly