The importance of voice AI and immersive audio in home entertainment, automotice infotainement and smartphones has led Cadence to announce its sixth generation of optimised DSP IP, the Tensilicia HiFi iQ DSP, which is purpose-built for on-device voice AI and audio. The latest addition to the HiFi DSP family is based on a purpose-built architecture designed and has double the ...

EDA and IP

Synopsys sells Processor IP to GlobalFoundries

Synopsys has sold its Processor IP Solutions business to GlobalFoundries for an undisclosed sum. It follows the MIPS acquisition in August, which added its Risc-V IP software and tools to the foundry’s services. The Synopsys Processor IP Solutions business includes ARC-V (Risc-V) and ARC CPU IP, DSP IP, NPU (network processing unit) IP, software development tools, including ARC MetaWare development ...

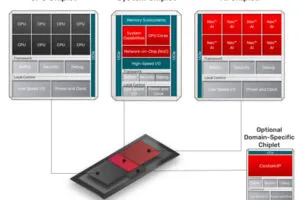

Cadence and IP partners provide pre-validated packaged chiplets

At CES 2026, Cadence announced an ecosystem which delivers pre-validated (spec-to-packaged parts) for physical AI, data centre and HPC (high performance computing). In Las Vegas, Cadence announced that Arm, Arteris, eMemory, M31 Technology, Silicon Creations and Trilinear Technologies are IP partners for the Physical AI chiplet platform and chiplet framework. The ecosystem also includes silicon analytics partner proteanTecs. A silicon ...

CES: RISC-V AI neural processor IP from MIPS

MIPS unveiled AI neural processor intellectual property based on RISC-V at CES, intended to support transformer and agentic language AI models at the edge. Called MIPS S8200, “it combines tightly coupled AI engines with RISC-V application cores to accelerate both vector and matrix workloads, supporting PyTorch and Tensor frameworks and scaling from tens to hundreds of TOPS via coherent cluster ...

Camera reference design delivers 4K AI inference

The 4Kp30 multi-sensor camera reference design is by Altera and designed for its Agilex 5 FPGAs. It uses industry-standard MIPI connectivity: D-PHY and MIPI CSI-2 for the FPGA interface and Altera’s FPGA AI tool for smart camera development to develop glass-to-glass edge vision for smart cameras, with real-time 4K AI interference. The MIPI interface supports up to 2.5Gbps per lane ...

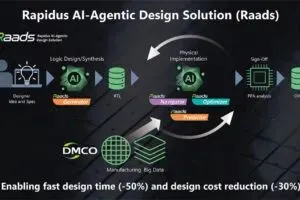

Rapidus launches design tools

Rapidus has announced a suite of AI design tools to support its Rapidus AI-Assisted Design Solution (Raads), a key initiative to helping to realise its Rapid and Unified Manufacturing Service (RUMS) concept. The technology approach will also be rebranded to Rapidus AI-Agentic Design Solution with multiple tools being released starting in 2026 and will be provided to customers together with ...

£5m for CHERI commercialisation

EnSilica, the mixed-signal asic specialist, has been awarded a £5m ‘contract for innovation’ by the UK government’s Department for Science, Innovation and Technology (DSIT). The funding furthers commercialisation of Capability Hardware Enhanced Risc Instructions (CHERI). EnSilica’s commercial-off-the-shelf (COTS) CHERI-compliant secure processor chip, developed under the contract, will target quantum-resilient applications requiring the highest levels of security and functional safety, with ...

Flexlets – configurable chiplets – introduced

Socionext has introduced a new semiconductor product class of configurable chiplets which it calls Flexlets. As traditional monolithic SoC designs face physical and economic limits – reticle size constraints, yield challenges, and thermal bottlenecks – the industry is turning toward chiplet-based design, where designers can integrate their core features and interface functionalities, provided as chiplets, into a packaged device to ...

Red Semi launches Ordo1

RED Semiconductor has launched Ordo1, a new IP core designed for RISC‑V processors, and announced its membership in RISC‑V International. Ordo1 is a versatile AI and flow control accelerator, based on RED’s VISC architecture, aimed at enabling energy‑efficient, high‑performance edge AI applications across multiple industries. “Ordo1 represents a step-change in delivering high‑performance AI at the edge, where power and efficiency ...

RISC-V processors certified up to ASIL-D

TÜV SÜD has ASIL certified two RISC-V processors for ISO 26262 automotive functional safety: Codasip’s L735 up to ASIL-B, and its L739 up to ASIL-D. “In addition to functional safety certification, both products are also compliant with ISO/SAE 21434, the international standard for cybersecurity in automotive development,” according to Codasip. Both cores have a multi-issue in-order microarchitecture. L735 includes error-correcting ...

Electronics Weekly

Electronics Weekly